In a significant advancement for electronic design automation, researchers have developed a novel algorithm aimed at generating pseudo-datasets for integrated circuit (IC) power analysis. The study, led by a team from the College of Information Science and Electronic Engineering at Zhejiang University in collaboration with Shanghai Hexin Industrial Software Co., Ltd., addresses the pressing need for comprehensive datasets in the increasingly data-driven landscape of machine learning (ML) applications within the IC industry.

Current datasets used in power analysis often fall short, lacking both the quantity and specificity required for effective machine learning applications. Moreover, accessing extensive industrial data frequently encounters legal challenges, including copyright issues, making it difficult for researchers and engineers to obtain necessary information. This new algorithm aims to overcome these obstacles by creating pseudo-circuit datasets that can be used for power analysis without the constraints tied to actual industrial data.

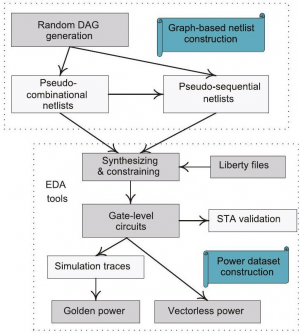

Zejia LYU, Jizhong SHEN, and Xi CHEN detail their approach in the paper titled “Algorithm and Evaluation of Generating Pseudo-Datasets for Integrated Circuit Power Analysis.” Their method employs a graph topology-based pseudo-circuit generation algorithm. It begins by converting randomly generated directed acyclic graphs (DAGs) into gate-level Verilog pseudo-combinational circuit netlists, allowing for the efficient creation of numerous power analysis examples.

In this process, register units are integrated to transform the pseudo-combinational netlists into pseudo-sequential circuit netlists. The researchers utilize hyperparameters to manage the circuit topology, applying appropriate sequential constraints during synthesis to create a robust pseudo-circuit dataset. This structured approach ensures a diverse range of circuit examples to facilitate comprehensive power analysis.

To evaluate the effectiveness of their algorithm, the team employed mainstream power analysis software, including Synopsys PrimeTime PX and Cadence Voltus. Pre-layout average power tests were conducted on the generated circuits, which were then compared with benchmark datasets. The results demonstrated strong consistency in power consumption distribution trends between the generated pseudo-datasets, which include 1,000 sets of combinational and 1,000 sets of sequential circuit netlists, and the benchmark datasets.

The research highlights the operational efficiency and robustness of the proposed algorithm. Notably, the parallel generation of samples significantly reduces time overhead, making the approach not only innovative but also practical for widespread usage. Additionally, a unique feature allows users to adjust the sequential circuit generation factor α, enabling control over circuit topology and addressing challenges such as the zero-value phenomenon in sequential circuit power analysis.

The findings underscore the algorithm’s potential to transform IC power analysis and enhance the capabilities of electronic design automation. With the growing integration of machine learning methods in this field, access to comprehensive and specific datasets will be crucial for future advancements.

The full text of the paper can be accessed at [https://doi.org/10.1631/FITEE.2400677](https://doi.org/10.1631/FITEE.2400677).