Researchers at the Massachusetts Institute of Technology (MIT) have unveiled a groundbreaking superconducting nanowire memory array with a remarkably low error rate of approximately 1 in 100,000 operations. This innovation, detailed in a study published on January 25, 2026, in the journal Nature Electronics, represents a significant advancement in the development of energy-efficient memory components essential for future quantum computing.

Superconducting memories, utilizing materials that exhibit zero electrical resistance when cooled below a critical temperature, have the potential to outperform traditional memory technologies in both speed and energy consumption. However, previous iterations have struggled with high error rates and scalability, limiting their practical application.

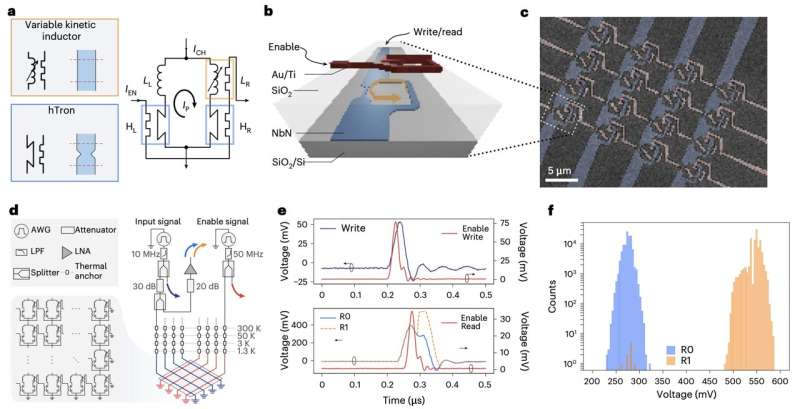

The research team, led by Owen Medeiros and Matteo Castellani, focused on creating a scalable superconducting memory using one-dimensional (1D) nanowires, which possess unique optoelectronic properties. They developed a compact 4 × 4 array of superconducting memory cells designed for efficient row-column operations, achieving a functional density of 2.6 Mbit cm −2.

Design and Functionality of the Memory Array

Each memory cell in the newly developed array consists of a superconducting nanowire loop equipped with two switches and a kinetic inductor. The operation of the switches varies with temperature, allowing for a stable memory function by managing electrical current flow predictably. The researchers noted, “The arrays operate at 1.3 K, where we implement and characterize multiflux quanta state storage and destructive read-out.”

Data is written and read in this system through precisely timed electrical pulses directed at specific cells. When a pulse is applied, it temporarily heats one of the nanowire switches, altering its resistance and injecting a magnetic flux into the loop. This magnetic flux encodes the information as binary values (0 or 1). After the pulse concludes, the nanowire returns to a superconducting state, effectively trapping the encoded information.

Implications for Quantum Computing

Initial tests of this superconducting memory array indicate a significant improvement in error rates, achieving a minimum bit error rate of 10 −5. The research team utilized circuit-level simulations to explore the dynamics, performance limits, and stability of the memory cell under varying conditions.

The advancement made by Medeiros, Castellani, and their colleagues could pave the way for more reliable superconducting memory systems, which are critical for the evolution of low-energy superconducting and fault-tolerant quantum computers. As the researchers stated, “Scalable superconducting memory is required for the development of low-energy superconducting computers and fault-tolerant quantum computers.”

This significant achievement not only enhances our understanding of superconducting materials but also brings the practical use of superconducting memories closer to reality. Future improvements to this design could lead to even more efficient and reliable memory systems, further driving innovation in the field of quantum computing.